#BZOJ2543. 逻辑电路最优设计

逻辑电路最优设计

题目描述

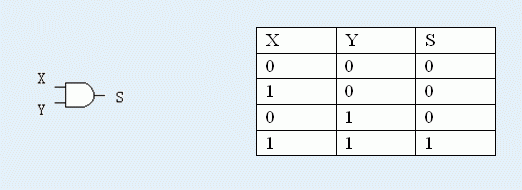

上图中,如果“与门”的两个输入端X和Y都是高电平“1”,则输出端S也是高电平“1”,否则,输出端S是低电平“0”。 <o:p></o:p>

假定,本次实验提供的门电路都具有输入对称性,即交换两个输入端的信号,输出不变。但是,如果门电路的输入端悬空(即没有加输入信号),则输出无意义。 <o:p></o:p>

<o:p> </o:p>

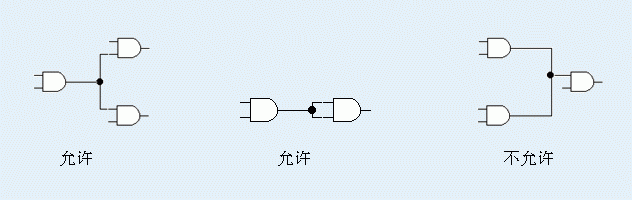

在连接电路的过程中,一个门电路的输出端可以将信号送到其他多个元件的输入端;而门电路的一个输入端则只能接收来自一个输出端的信号。如下图所示: <o:p></o:p>

<o:wrapblock>

<v:shapetype id="_x0000_t202" coordsize="21600,21600" o:spt="202" path="m,l,21600r21600,l21600,xe">

<v:stroke joinstyle="miter"></v:stroke>

<v:path gradientshapeok="t" o:connecttype="rect"></v:path>

</v:shapetype>

</o:wrapblock>

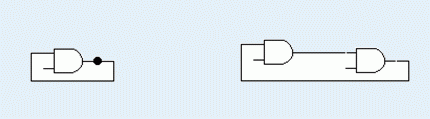

另外,规定信号必须单向传输,即一个门电路的输出不能直接或间接通过其他门电路回到同一门电路的输入端。如下图所示即为两种不允许的连接方式:

<o:p></o:p>

<o:wrapblock>

<v:shapetype id="_x0000_t202" coordsize="21600,21600" o:spt="202" path="m,l,21600r21600,l21600,xe">

<v:stroke joinstyle="miter"></v:stroke>

<v:path gradientshapeok="t" o:connecttype="rect"></v:path>

</v:shapetype>

<v:shape id="_x0000_s1026" type="#_x0000_t202" stroked="f" style="margin-top: 73pt; z-index: 1; left: 0px; margin-left: 45pt; width: 4in; text-indent: 0px; position: absolute; height: 70.2pt; text-align: left; mso-position-vertical-relative: page">

<v:textbox style="mso-next-textbox: #_x0000_s1026"></v:textbox>

<w:wrap type="topAndBottom" anchory="page"></w:wrap>

</v:shape>

</o:wrapblock>

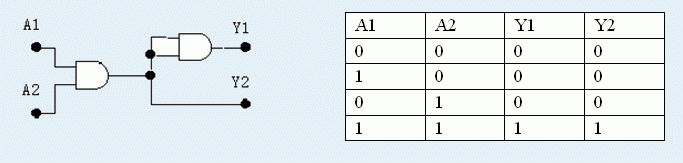

要求你设计的译码电路是一个有四个输入端和四个输出端的逻辑电路,该译码电路的输入和输出关系通过功能表给出,即给出每种输入组合下的四个输出端的情况。显然,一共有 2^4=16种输入组合。比如,一个由前述“与门”构成的2输入,2输出的简单译码电路如下图所示(其中,A1, A2是输入端,Y1, Y2是输出端):

输入格式

其中第一行为一个正整数N,N<=5,表示元件的种类数,其后有连续的N行,每行描述一种元件。对正整数1<=K<=N <o:p></o:p>

文件的第K+1行有四个以空格隔开的整数,依次为: <o:p></o:p>

Mk Y00 Y01 Y11 <o:p></o:p>

其中,正整数Mk表示第K种元件的数目(K即这种元件的种类编号),所有元件的数目之和不会超过10(用于实验的经费并不充足)。Yij表示两个输入端分别为i和j时的输出,即Y00,Y01,Y11是三个非0即1的数,分别表示在两个输入端均为0;两个输入端一个为0另一个为1;以及两个输入端均为1的时候,该元件的输出。 <o:p></o:p>

输入文件的第N+2到第N+17行,表示需组成的集成电路的功能表,每行有8个数,分别为0或1。其中,前四个数依次对应四个输入端(编号为1~4)的信号,不存在两行的前四个数完全相同;而后面四个数则对应在各输入端信号为前四个数时,四个输出端依次应输出的信号。 <o:p></o:p>

输出格式

文件的第一行为一个单词,“Yes”或“No”——如果存在符合要求的设计方案,则为“Yes”,否则为“No”。 <o:p></o:p>

如果第一行是“No”,则文件结束,否则—— <o:p></o:p>

第二行只有一个非负整数p,表示最少需要的门电路数目。下面p行分别给出每个门电路在电路中的连接情况的描述。每行有四个以空格隔开的正整数:S K A B,其中S表示该门电路的编号(所有用到的门电路按5~p+4编号,1~4的编号用来表示四个输入端);K表示该元件的种类编号(按照输入文件中的顺序由1~ <v:shapetype id="_x0000_t75" coordsize="21600,21600" o:spt="75" path="m@4@5l@4@11@9@11@9@5xe" stroked="f" o:preferrelative="t" filled="f"> <v:stroke joinstyle="miter"></v:stroke> <v:formulas> <v:f eqn="if lineDrawn pixelLineWidth 0"></v:f> <v:f eqn="sum @0 1 0"></v:f> <v:f eqn="sum 0 0 @1"></v:f> <v:f eqn="prod @2 1 2"></v:f> <v:f eqn="prod @3 21600 pixelWidth"></v:f> <v:f eqn="prod @3 21600 pixelHeight"></v:f> <v:f eqn="sum @0 0 1"></v:f> <v:f eqn="prod @6 1 2"></v:f> <v:f eqn="prod @7 21600 pixelWidth"></v:f> <v:f eqn="sum @8 21600 0"></v:f> <v:f eqn="prod @7 21600 pixelHeight"></v:f> <v:f eqn="sum @10 21600 0"></v:f> </v:formulas> <v:path gradientshapeok="t" o:connecttype="rect" o:extrusionok="f"></v:path> <o:lock v:ext="edit" aspectratio="t"></o:lock> </v:shapetype> <v:shape id="_x0000_i1025" type="#_x0000_t75" o:ole="" style="width: 9.75pt; height: 11.25pt"> <v:imagedata src="file:///C:\DOCUME~1\ADMINI~1\LOCALS~1\Temp\msohtml1\01\clip_image001.wmz" o:title=""></v:imagedata> </v:shape>编号);A和B分别表示接入该元件的两个输入端的门电路或译码电路输入端的编号(其中,A<S,B<S)。 <o:p></o:p>

最后一行有四个正整数,表示组成的译码电路的四个输出端分别所接的元件的编号(在1~p之间)。 <o:p></o:p>

1

5 0 1 0

0 0 0 0 0 0 0 0

1 0 0 0 1 0 0 0

0 1 0 0 1 1 0 0

1 1 0 0 0 1 0 0

0 0 1 0 0 1 1 0

1 0 1 0 1 1 1 0

0 1 1 0 1 0 1 0

1 1 1 0 0 0 1 0

0 0 0 1 0 0 1 1

1 0 0 1 1 0 1 1

0 1 0 1 1 1 1 1

1 1 0 1 0 1 1 1

0 0 1 1 0 1 0 1

1 0 1 1 1 1 0 1

0 1 1 1 1 0 0 1

1 1 1 1 0 0 0 1

Yes

3

5 1 2 1

6 1 3 2

7 1 4 3

5 6 7 4